## Sub-100nm Ferroelectric-gate Thin Film Transistor Fabricated by Two-patterning Method

Do Hong Minh\*, Pham Duc Thang and Bui Nguyen Quoc Trinh

Vietnam National University, VNU University of Engineering and Technology, Faculty of Engineering Physics and Nanotechnology, Building E4, 144 Xuan Thuy, Cau Giay, Hanoi, Vietnam

minhdh.dl12@vnu.edu.vn

## **Short notes:**

ERATO Exploratory Research for Advanced Technolog 电影中 (超版集集型等)

a sub-100nm FGT

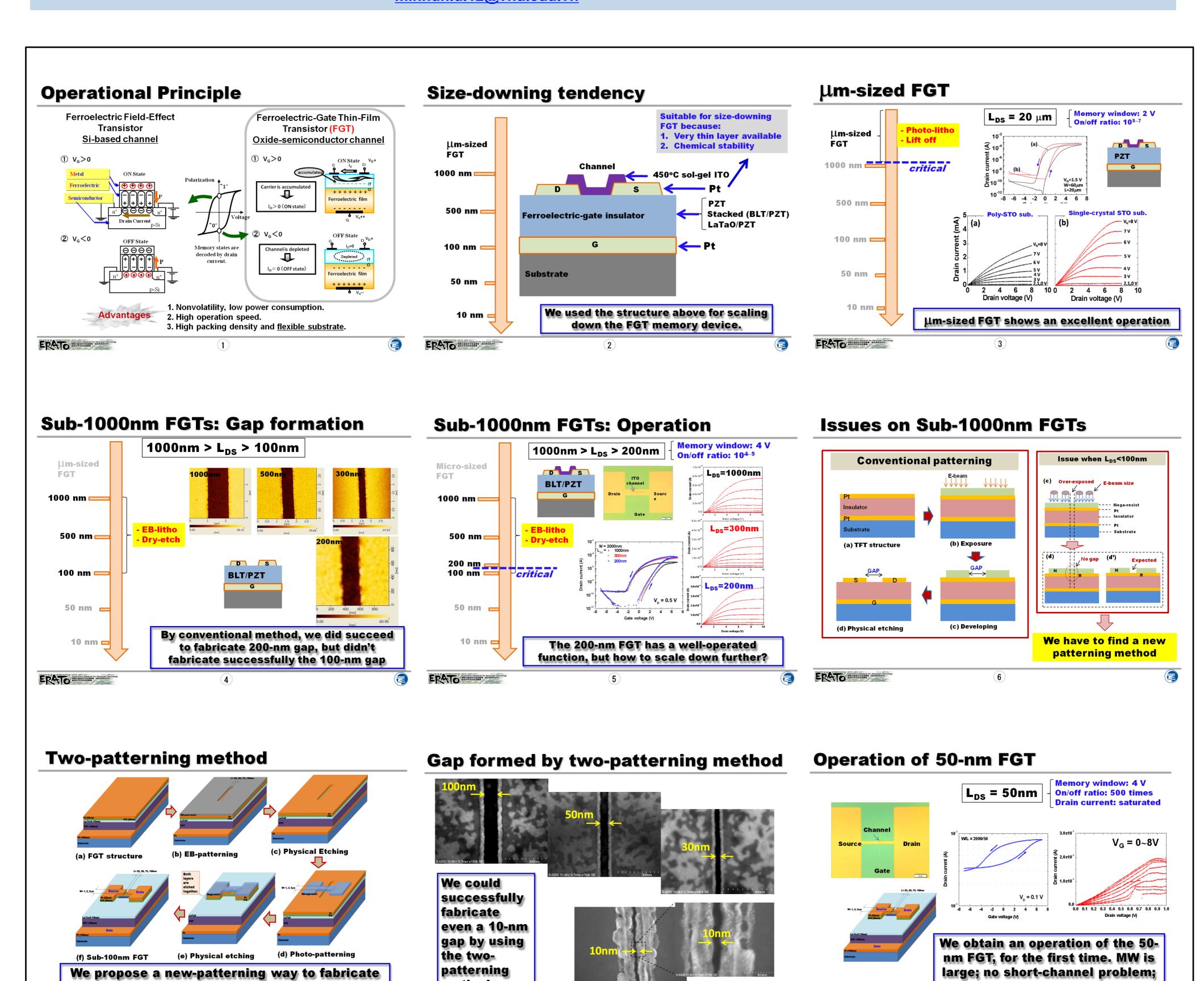

1. We propose a new-patterning way (so-called a two-patterning method) to fabricate sub-100nm FGTs. Up-to-10nm FGT gap could be successfully created under an assistant of the dry-etching technique.

method

ERATO Epioratory Research for Advanced Technolog

- 2. By using the two-patterning method, we solve essentially the difficulties from the conventional method. As a result, we demonstrate an operation of the 50-nm FGT.

- 3. Taking a comparison with the  $\mu$ m-sized and the sub-1000 nm FGTs, the on/off ratio of the sub-100 nm FGT is much smaller. Therefore, further work should be carried out to improve and demonstrate a FGT with a size downed to 10 nm.

## Acknowledgement

The authors would like to thank Dr. Yamaguchi at Tokyo Institute of Technology in Japan for his co-operation work of e-beam lithography process.

but the on/off ratio is small

ERATO Exporatory Research for Advanced Technology