# Design of a C-Band Low-Noise Block Front-end for Satellite Receivers

### Tran Van Hoi

Faculty of Electronics and Communications Technology, Broadcasting College 1, Voice of Viet Nam, Ha Nam, Viet Nam

## **Nguyen Xuan Truong**

Faculty of Electronics and Communications Technology, Broadcasting College 1, Voice of Viet Nam, Ha Nam, Viet Nam

## Ngo Thi Lanh

Faculty of Electronics and Communications Technology, Broadcasting College 1, Voice of Viet Nam, Ha Nam, Viet Nam

## **Bach Gia Duong**

Electronics and Telecommunications Center, Faculty of Electronics and Telecommunications University of Engineering and Technology, Viet Nam National University, Ha Noi, Viet Nam

#### **Abstract:**

This paper describes the study, design and fabrication of a C-band low-noise block front-end for satellite receivers. The front-end consists of a low-noise amplifier, two band pass filters in C-band and L-band, a down-converter and an intermediate frequency amplifier. To reduce noise figure and increase bandwidth, the low-noise amplifier was designed using T-type of matching network with negative feedback. The down-converter used a voltage controlled oscillator with phase locked loop to reduce the phase noise. The front-end converts input signals from C-band (3.4 GHz-4.2 GHz) to the L-band (950 MHz-1750 MHz). The low-noise block has successfully been designed and fabricated with parameters: Overall gain is greater than 60 dB; the noise figure is less than 1dB; phase noise of local oscillator obtains-107.57dBc/Hz at 50KHz.

**Keywords:** Bandpass filter, Low noise block, Low noise amplifier, Voltage controlled oscillator, Satellite communication

## Introduction

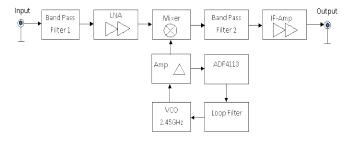

A low-noise blockdown-converter (LNB) is a part of a receiver system, which is used for the satellite communication or wireless communications service. It is the device in front of a satellite dish to pick up very low-level microwave signals from the satellite, then amplifying it, converting to lower frequency bands. The output signals are sent to an in-door settop box for finer channel selection. A diagram of the low-noise block front-end can be found in Fig.1. Input signals to a LNB are polarized vertical or horizontal togo through abandpass filter, only allowing the intended band of microwave frequencies to pass through. Then signals are amplified by alow-noise amplifier (LNA), after that go to the mixer. At the mixer, output signals are in the L-band to come through the

second bandpass filter and feed them to the intermediate frequency (IF) amplifier.

This work demonstrates a design and implementation of a down-converter front-end used for C-band satellite receivers. To design a front-end receiver with the best characteristic in the entire system, we have to solve those major challenges remain. The first of them is to achieve a low-noise figure (NF), higher gain and sufficient bandwidth. Some resultswere publicated to optimize parameters of LNA and local oscillator [1]-[3]. In the proposed design, a two-stage LNA and IF amplifier using discrete pHEMT amplifiers can accomplish this goal. The first-stage amplifier was designed using negative feedback with T-type of matching network to reduce noise figure and increase bandwidth. The second stage is designed for high gainand wideband. The second challenge is to achieve low phase noise, spurious free signal with a sufficient power level of voltage controlled oscillator (VCO) [3], [4]. Therefore, the local oscillator use voltage controlled oscillator combine phase locked loop frequencysynthesizer and a single-stage amplifier.

Under these conditions, the paper is organized as follows. Section 2 describes the design and simulation of LNB. Section 3 presents the fabrication and experimental results. Section 4 summarizes the conclusions of the presented work.

Figure 1: Low-noise block front-end diagram.

## Design of a Bandpass filters

At the input reveiver, the first bandpass filter (BPF1) has a center frequency of 3.8 GHz with passband from 3.4 GHz to 4.2 GHz or fractional bandwidth of 21%. The second bandpass filter (BPF2) passes the frequency from 0.95GHz to 1.75GHz, so it has a center frequency of 1.35GHz and fractional bandwidth of 60% [6].

There are some method designs of bandpass filters such as: End-coupled, parallel-coupled, hairpin, interdigital and stub bandpass filters... However, the hairpin bandpass filter was chosen, because it has open-circuited ends and compact configuration.

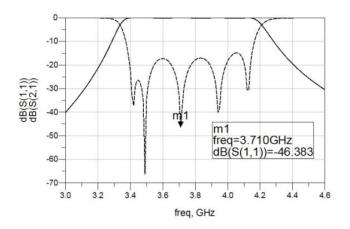

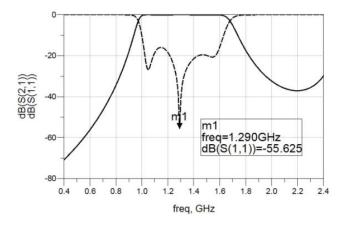

The Chebyshev filter and FR4 substrate was chosen with parameters: five-pole and ripple of 0.1dB, substrate height 1.5 mm, loss tangent is 0.001 and dielectric constant is 4.34. A procedure of the design can be found in [7], the simulated results shown in the fig 2 and 3.

Figure 2: Simulated results of S21 and S11 at 3.8 GHz

Figure 3: S21 and S11 at 1.35 GHz

# Design of a low noise amplifier

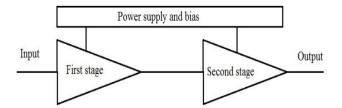

In order to achieve bandwidth 800 MHz and high gain, we suppose the design of the LNA has two-stage cascade amplifier based on the design of single-stage one. The center frequency in the first stage is 3.7 GHz and the second stage is 3.9 GHz. The configuration of two-stage cascade LNA illustrated the Fig.4.

Figure 4: Diagram of two-stage cascade LNA

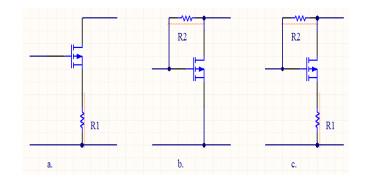

This two-stage amplifier was designed using T-type of matching network at the input and output terminal. However, The negative feedback can be used in broadband amplifiers to create a linear, flat gain response and lower input and output VSWR [8]. Thus, the first stage used negative feedbackcircuit to degrade the noise figure and increase stable, bandwidth. The most common methods of negative feedback technique are the shunt and series resistor configuration shown in fig. 5 [8]. The negative feedback technique proposed by Gozalez was selected for this work.

Figure 5: GaAs FET negative feedback

The value of R<sub>1</sub> and R<sub>2</sub> can be calculated from followed equation [8].

$$R_{1} = \frac{Z_{0}^{2}}{R_{2}} - \frac{1}{g_{m}}$$

$$g_{m(min)} \frac{1 - S_{21}}{Z_{0}}$$

$$R_{2} = Z_{0} (1 + |S_{21}|)$$

(1)

(2)

$$\mathcal{G}_{m(min)} \frac{1 - \mathcal{S}_{21}}{Z_0} \tag{2}$$

$$R_2 = Z_0(1 + |S_{21}|) (3)$$

From equation (3), it can be seen that  $S_{21}$  depends only on  $R_2$ and not on the transistor parameters. Therefore, gain flattening can be achieved by negative feedback. When using the negative feedback, the phase of S<sub>21</sub> has a portion where the output voltage is in phase with the input voltage. So, to solve this problem, an inductor is often connected in series with  $R_2$ . The SPF-3043 transistor with low noise figure and high associated gain was chosen for the amplifier design. Applying the negative feedback equation and the help of a computer aid design (CAD) tool to calculate S-parameter of the feedback networkand the noise figure (4).

$$F = F_{\min} + \frac{4R_N}{Z_o} \left( \frac{\left| \Gamma_{opt} - \Gamma_s \right|^2}{\left| 1 + \Gamma_{opt} \right|^2 (1 - \left| \Gamma_s \right|^2)} \right)$$

(4)

The S-parameter is then used for the design of the input and output matching networks using Smith chart [9]. To obtain the minimum noise figurein the first stage, the reflection coefficient  $\Gamma_S$  look into the source is equal to  $\Gamma_{opt}$ , where  $\Gamma_{in}$  is set to be the conjugate of  $\Gamma_S$  and  $\Gamma_{out}$  is set to be the conjugate of  $\Gamma_L$ .

In the second stage, it will be designed to obtainthe maximum gain. In order to transfer the maximum power from the input matching networks to the transistor will occur when  $\Gamma_S = \Gamma^*_{in} = S^*_{11}$  and the maximum power transfer from the transistor to the output matching network will occur when  $\Gamma_L = \Gamma^*_{out} = S^*_{22}$ .

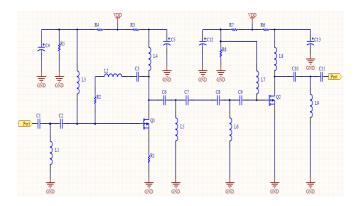

The completed LNA with two stages was shown in Fig.6. To meet the high IIP3 (third order input intercept point), the transistor will be biased at  $I_{DS}=30 \text{mA}$ ,  $V_{DD}=5 \text{V}$  and  $V_{GS}=-0.3 \text{V}$ .

Figure6: Schematic of the two-stage cascade LNA

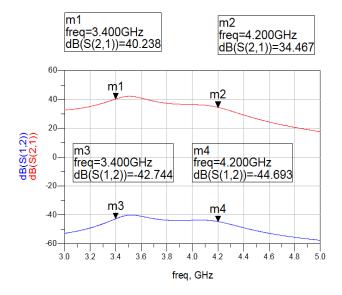

The initial simulations to test the LNA performance were done with the S-parameter file of the transistorwith ADS software. The Fig.7displays the  $S_{21}$  parameter which has been achieved: overall gain is greater than 34 dB from 3.4 GHz to 4.2 GHz and the value of reverse isolation ( $S_{12}$ ) is very good in working band.

Figure 7: The S21 and S12 of the LNA.

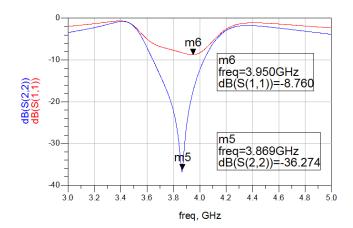

Figure 8: The S11 and S22 of the LNA

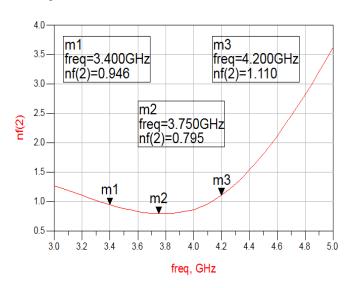

The result in Fig.8shows the value of the input impedance matching is quite good at from 3.4 GHz to 4.2 GHz. Although, the output impedance matching is very good at 3.869 GHz, but impedance matching range is very narrow. The noise figure is less than 1.110dB in workband.

Figure9: The noise figure of the amplifier

Similarly, the IF amplifier also designed using a two-stage cascade amplifier which based on the design of single-stage one. The center frequency of the first stage IF amplifier is 1.3GHz and the second stage is 1.5GHz. The input and output matching networks are designed to obtain a maximum gain. The VCO amplifier is designed using a narrow-band amplifier at the center frequency of 2.45GHz

# Design of the voltage controlled oscillator and mixer

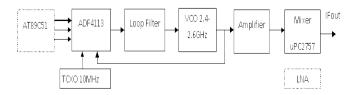

The voltage controlled oscillator (VCO)produces a fixed output frequency and must have extremely high stability as well as satisfying amplitude (in dBm). The design specifications of the VCO operates at 2.45 GHz to create the intermediate frequency output ranging from 950MHz to 1750MHz. A structure of the VCO can be found in Fig.10.

Figure 10: The architecture of the PLL synthesizer.

In order to stable oscillator frequency, our solution uses monolithic integrated synthesizer ADF4113 from Analog Devices. This part has been designed to implement local oscillators in the up-conversion and down-conversion sections of wireless receivers and transmitters. The ADF4113 includes a low-noise digital phase frequency detector, a precision chargedpump, a programmable reference divider, a dual modulus prescaler and two programmable counters. Data are transferred into the synthesizer by a three-wire serial interface. The advantages of this part are low current consumption at low supply voltage and small dimensions (TSSOP16 package).

The frequency of the reference oscillator TCXO placed on the board is 10 MHz. The ADF4113 includes a 24 bit input shift register, 14 bit R counter, and 19 bit N counter comprised of a 6 bit A counter and a 13 bit B counter. The loop filter was designed for an RF output of 2.45GHz, a PFD frequency of 1 MHz, a prescaler value of 16/17. The lock detector indicates the lock state of the PLL.The VCO CVCO33BE-2400-2500 from Crystek Corporation is selected. Supply voltage and tuning voltage of the VCO is 5VDC, which is the same supply voltage of ADF4113.

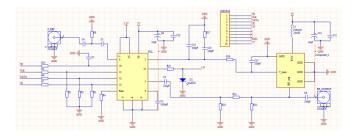

Low noise block down-converter utilizes the heterodyning technique to down-convert the S, C, Ku frequency to the IF. It mixes an internal fixed frequency with the incident one, and the output is a series of signals at the sum and the difference of the two inputs to the mixer. A mixer is a three-port device that uses a nonliner element to achieve frequency conversion. Operation of single-ended mixers used a monolithicintegrated circuit uPC2757TB from California Eastern Laboratories. The schematic of VCO can be found in Fig.11.

Figure 11: The schematic of VCO

## **Experimental results**

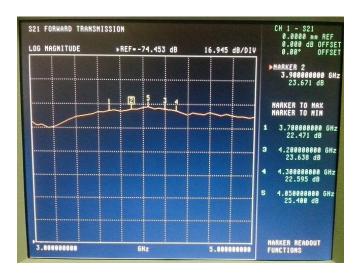

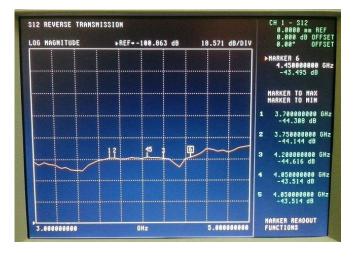

The LNB has been tested, and the consequent measurements on the Network Analyzer 37369D have confirmed the designed parameters. The fig.12 determines the maximum gain of LNA is25.4 dB at 4.05 GHz and circuit amplifies wideband from 3.4 to 4.2 GHz with gain is greater than 22 dB,

compared to 20dB of paper [10] when using quarter wave transformer matching.

The Fig.13 shows that the reverse isolation is good agreement between the simulated and measured results can be observed.

Figure 12: The gain of the LNA

**Figure 13:** The reflection coefficient S12

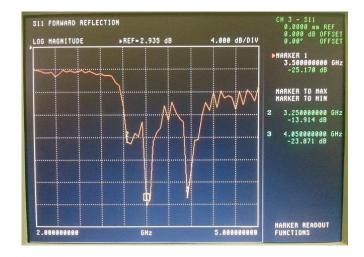

Figure 14: The input reflection coefficient S11

Looking into the results in Fig. 14 and 15, both simulated and measured results show the similar response. Whereas the measured  $S_{11}$  resonates at 3.5 GHz and 4.05 GHz, compared to 3.7 GHz and 4.0 GHz of the simulation. However, the measured results have been observed to be greater than simulation.

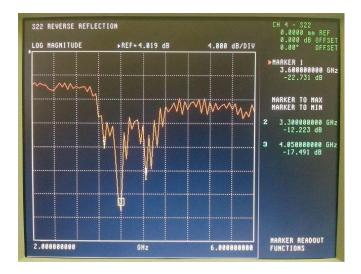

Figure 15: The output reflection coefficient  $S_{22}$

The magnitude of  $S_{22}$  clearly illustrates the quite good output impedance matching. Although the measured results have impedance matching to be larger than simulation, but they both display  $S_{22}$  value are acceptable and satisfy the requirement set.

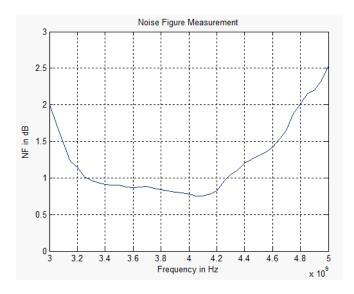

Figure 16: Noise Figure Measurement

Fig. 16 shows the noise figure measurement, the noise figure of 0.85 dB is from 3.4 GHz to 4.2 GHz. This value shows that noise figure was enhanced by using negative feedback circuit in the first-stage amplifier, compared to 1.2 dBof paper [10] when not using feedback circuit.

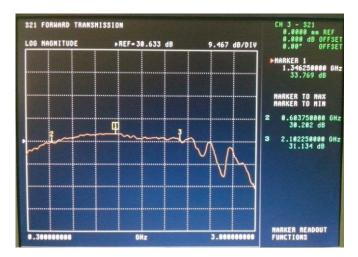

Similarly, intermediate frequency amplifier has been tested on the Network Analyzerwith maximum gain is33.769 dB at 1.346GHz and circuit amplifies wide band from 0.6 to 2.1 GHz with gain is greater than 30dB.Due to matching networks are designed to obtain a maximum gain.

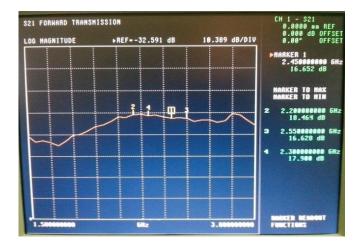

The VCO amplifier has been testedwith gain is 16.652dB at 2.45GHz and input impedance matching is quite good.

Figure 17: The gain of the IF amplifier

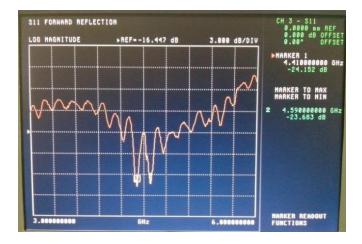

Figure 18: The input reflection coefficient  $S_{11}$

Figure 19: The gain of the VCO amplifier

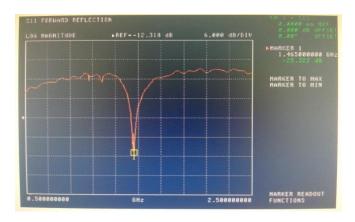

Figure 20: The output reflection coefficient  $S_{22}$

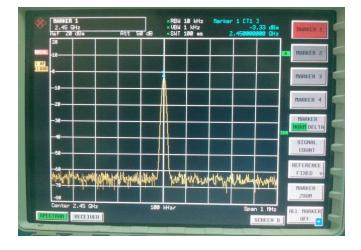

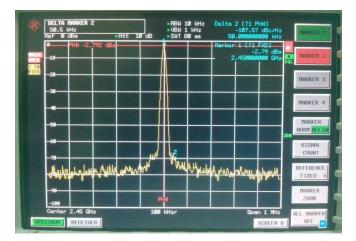

The achieved results of the oscillator circuit are all performed using spectrum analyzer NS-265 from 9 KHz to 26.5 GHz meeting the requested command about stability and amplitude. Figure 20, 21 have shown that the power of the oscillator is-3.33 dBm at 2.45 GHz and the power of VCO amplifier is 12.46dBm with the phase noise reaches-107.55 dBc/Hz at 50KHz. This value is better than the VCO using discreteelements in paper [10].

**Figure 21:** The result on the spectrum analyzer

Figure 22: The phase noise at 50KHz

Table 1 shows comparison results of recently LNBs. The proposed method provides available wideband, high gain with low phase noise.

**Table 1:** Comparison of recently LNBs

| Parameters  | Ref. [10]     | Ref. [11]    | This work     |

|-------------|---------------|--------------|---------------|

| Input       | 3.4GHz-4.2GHz | 1.26GHz-     | 3.4GHz-4.2GHz |

| frequency   |               | 1.268 GHz    |               |

| Output      | 0.95GHz-      | 247MHz       | 0.95GHz-      |

| frequency   | 1.75GHz       |              | 1.75GHz       |

| Overall     | 41dB          | 37 dB        | 60dB          |

| gain        |               |              |               |

| Local       | 2.45GHz       | 1.022 GHz    | 2.45GHz       |

| oscilator   |               |              |               |

| Phase noise | -108.63dBc/Hz | -103.3dBc/Hz | -107.57dBc/Hz |

|             | at 100KHz     | at 50KHz     | at 50KHz      |

#### Conclusion

This research presented design and fabrication aC-band lownoise block frond-end for satellite receivers. The paper also proposed methods to increase gain, bandwidth and decrease noise figure by using negative feedback circuit and optimized matching networks in the first stage of LNA. Besides,the VCO circuit used PLLfrequency synthesizer to increase phase noise. The results show that the LNBs had better performances inoverall gain, noise figure and phase noise of local oscillator. This LNB was using in the Vinasat satellite receiverswith automatic detection mechanism and auto tracking satellite [12].

### References

- [1] A. F. Osman, N. Mohd. Noh, "Wideband Low Noise Amplifier Design for Software Defined Radio at 136 to 941 MHz," 4th International Conference on Intelligent and Advanced Systems (ICIAS2012), 2012, pp. 232-236.

- [2] Kamil P., Abdul R. O., Zahriladha Z., Mohamad K. S., Abdul H.H., J.S. Hamidon, Azman A. "Design and Analysis High Gain PHEMT LNA for Wireless Application at 5.8 GHz", *International Journal of Electrical and Computer Engineering*, vol. 5, no.3, pp 611-620, 2015.

- [3] Tran Van Hoi, Hoang Duc Long, Bach Gia Duong, ''High gain low noise amplifier design used for RF front end application'', *The 2013 IEICE International Conference on Intergrated Circuits, Design, and Verification*, 2013, pp. 243-247.

- [4] Li Zhigang, Ren Pengfei, "Design of L-Band PLL Frequency Synthesizer", *International Conference on Mechatronic Sciences, Electric Engineering and Computer (MEC)*, Dec 2013, Shenyang, China pp. 13-16.

- [5] Moon-Que Lee, Keun-Kwan Ryu, In-Bok Yom, "Phase Noise Reduction of Microwave HEMT Oscillators Using a Dielectric Resonator Coupled by

- a High Impedance Inverter", ETRI Journal, vol. 23, no. 4, pp. 199-201, 2011.

- [6] Tran Van Hoi, Bach Gia Duong, "Designing Wideband Microstrip Bandpass Filter for Satellite Receiver Systems", *National Conference on Electronics and Communications (REV2013-KC01)*, pp.140-143 Viet Nam 2013.

- [7] JIA-Sheng Hong, M. J. Lancester, "Microstrip Filters for RF/Microwave Application", *John Wiley & Sons, Inc,* New York, 2001, pp 121-158.

- [8] G. Gonzalez, "Microwave Transistor Amplifiers Analysis and Design", *Prentice Hall, 1997*, pp. 323-348.

- [9] Tran Van Hoi, Bach Gia Duong, "Study and design of wideband low noise amplifier operating at C band, *Journal of Mathematics-Physics, Vietnam National University*, vol. 29, no. 2, pp.16-24, 2013.

- [10] Tran Van Hoi, Hoang Duc Long, Bach Gia Duong, "Low noise block downconverter design for satellite receiver system Vinasat 1 operating at C-band", *The 2013 IEICE International Conference on Intergrated Circuits, Design, and Verification*, pp.110-115, 2013.

- [11] Kasal, M., Kutin, P., Zamazal, M., Lakkundi, V, "Satellite L-Band Front End Design", WSEAS Transactions on Computers, 2004, vol. 3, iss. 6, pp.1907-1 910, 2004.

- [12] Tran Van Hoi, Nguyen Xuan Truong, Bach Gia Duong, "Improvement of step-tracking algorithm used for mobile receiver system via satellite", *International Journal of Electrical and Computer Engineering*. Vol. 5, No. 2, April 2015, pp. 280-288