# Materials Research Express

RECEIVED 16 August 2018

ACCEPTED FOR PUBLICATION

31 October 2018

PUBLISHED 14 November 2018

#### **PAPER**

# Si-doping effect on solution-processed In-O thin-film transistors

Ha Hoang¹, Tatsuki Hori¹, To-oru Yasuda², Takio Kizu³, Kazuhito Tsukagoshi³, Toshihide Nabatame⁴, Bui Nguyen Quoc Trinh⁵, and Akihiko Fujiwara¹,²

- Department of Physics, School of Science and Technology, Kwansei Gakuin University, 2-1 Gakuen, Sanda, Hyogo 669-1337, Japan

- Department of Nanotechnology for Sustainable Energy, School of Science and Technology, Kwansei Gakuin University, 2-1 Gakuen, Sanda, Hyogo 669-1337, Japan

- <sup>3</sup> International Center for Materials Nanoarchitectonics (WPI-MANA), National Institute for Materials Science (NIMS), 1-1 Namiki, Tsukuba, Ibaraki 305-0044, Japan

- <sup>4</sup> MANA Foundry and MANA Advanced Device Materials Group, National Institute for Materials Science (NIMS), 1-1 Namiki, Tsukuba, Ibaraki 305-0044, Japan

- Faculty of Engineering Physics and Nanotechnology, VNU University of Engineering and Technology, Vietnam National University, 144 Xuan Thuy, Cau Giay, Hanoi, Vietnam

- Nanotechnology Program, VNU Vietnam Japan University, Vietnam National University, Luu Huu Phuoc, Nam Tu Liem, Hanoi, Vietnam

E-mail: akihiko.fujiwara@kwansei.ac.jp

Keywords: silicon-doped indium oxide, thin-film transistor, spin coating, solution processing, amorphous oxide semiconductor

#### Abstract

In this work, silicon-doped indium oxide thin-film transistors (TFTs) have been fabricated for the first time by a solution processing method. By varying the Si concentration in the  $In_2O_3$ –Si $O_2$  binary oxide structure up to 15 at%, the thicknesses, densities, and crystallinity of the resulting In–Si–O (ISO) thin films were investigated by x-ray reflectivity (XRR) and x-ray diffraction techniques, while the produced TFTs were characterized by a conventional three-probe method. The results of XRR analysis revealed that the increase in the content of Si dopant increased the thickness of the produced film and reduced its density, and that all the Si-doped ISO thin films contained only a single amorphous phase even after annealing at temperatures as high as 800 °C. The manufactured ISO TFTs exhibited a reduction in the absolute value of threshold voltage  $V_T$  close to 0 V and low current in the off-state, as compared to those of the non-doped indium oxide films, due to the reduced number of oxygen defects, which was consistent with the behavior of ISO TFTs fabricated by a sputtering method. The ISO TFT with a Si content of 3 at% annealed at 400 °C demonstrated the smallest subthreshold swing of 0.5 V/dec,  $V_T$  of -5 V, mobility of 0.21 cm $^2$  V $^{-1}$ s $^{-1}$ , and on/off current ratio of about 2  $\times$  10 $^7$ .

## 1. Introduction

Recently, metal oxide semiconductors have attracted significant attention as potential materials for the next-generation electronic devices due to their high carrier mobility and optical transparency. In particular, doped indium oxides (In–O: IO) have been studied as channel materials for thin-film transistors (TFTs) that can be used in high-definition flat panel displays, owing to the excellent device characteristics of amorphous In-Ga-Zn-O compounds [1–3]. However, their resistance against external stress and scale-up capabilities require further improvement [2–5].

Because Si doping is able to effectively stabilize the amorphous structures of IO films and reduce the number of oxygen deficiencies due to the high dissociation energy of the Si-O bond, it can be potentially used for the reduction of a large negative threshold voltage  $V_T$ [6-9]. Therefore, Si-doped IO (In-Si-O: ISO) is a promising material for the fabrication of TFTs utilized in flat panel displays. Multiple studies on ISO and its properties were performed in the past [6, 10, 11]; however, no solution-processed ISO transistors have been reported yet. Using a spin coating method, the concentration of doped Si species can be easily changed by varying its content in solution, which allows investigation of the doping effect over a wide range of dopant concentration despite the slight reduction in the film quality. In this respect, spin coating is advantageous to another typical ISO deposition

method, DC sputtering, which requires fabrication of separate targets for each studied composition. Moreover, spin coating is a very practical method as compared to physical vapor deposition, because of its simplicity, low cost, easy control over chemical stoichiometry, and applicability to mass production [12–18]. In addition, a relatively large variety of substrates, including glass and plastic, can be utilized for solution processing.

Regarding to patterning, it is important to isolate each transistor to reduce the gate leak current and minimize the crosstalk between various devices. Lithography represents a widely used patterning technique, which, however, requires long processing times as well as the use of complicated procedures and special facilities such as cleanrooms. In contrast, a patterning technique based on the wetting properties of a material is expected to be much easier to implement [19–21]. To ensure good wetting, a hydrophobic surface must be matched with a non-polar solution, and a hydrophilic surface—with a polar solution. Although the surface of SiO<sub>2</sub> is naturally hydrophobic, it can be transformed to a hydrophilic one by the treatment with ultraviolet light, plasma, or chemical reagents [19, 20, 22]. Therefore, by controlling surface properties and selecting an appropriate solution, the patterning procedure can be performed more easily than the lithographic one, especially when combined with solution-based techniques such as spin coating, inkjet printing, and dip coating. To explore this possibility, the wetting properties of ISO films and their deposition on hydrophobic surfaces were investigated elsewhere [11].

In this study, ISO thin films and TFTs were fabricated for the first time on hydrophilic surfaces using polar solutions. The stabilization of their amorphous structures and improvement of device characteristics, such as the reduction of the absolute values of threshold voltage  $|V_T|$  (to magnitudes near 0 V) and off current, were similar to those observed for the ISO TFTs manufactured by the sputtering method [10].

# 2. Experimental methods

The solution processing technique described by Han et al [22] was modified to make it applicable for the fabrication of ISO films. Precursor solutions for spin coating were prepared by dissolving indium chloride (InCl<sub>3</sub>) powder (CAS: 10025-82-8) in acetonitrile (CH<sub>3</sub>CN) solvent (CAS: 75-05-8) at a molar concentration of 0.05 M. Acetonitrile is a solvent with a low boiling point and high evaporation rate; hence, it evaporates relatively fast during spin coating, leading to the formation of non-uniform films. Therefore, a small amount of high boiling point ethylene glycol solvent (HOCH<sub>2</sub>CH<sub>2</sub>OH; CAS: 107-21-1) was added to the InCl<sub>3</sub> solution at an ethylene glycol to acetonitrile a volume ratio equal to 1/50. As a result, uniformly coated films were obtained despite fast evaporation of the acetonitrile because the presence of ethylene glycol species allowed InCl<sub>3</sub> molecules to spread across the substrate surface. In addition, it was found that increasing the concentration of ethylene glycol in solution produced more inhomogeneous films due to the solvent-induced dewetting. For this reason, the solution should contain a greater fraction of the low boiling point solvent and a much smaller fraction of the high boiling point solvent. Because of low solubility of InCl<sub>3</sub> to acetonitrile, the solution was subsequently stirred at room temperature for at least 1 week using a magnetic stirrer to reach high degrees of uniformness and consistency. For Si doping, tetraethyl orthosilicate (TEOS; CAS: 78-10-4) was added to the reaction solution with Si contents to In of 3, 5, 10, or 15 at%. TEOS containing slution was sttirred for a few hours and folowed by spin coating as shown bellow; long time stirring of TEOS containing solution resulted in degradation of the solution.

SiO<sub>2</sub> (250 nm)/Si (high doped p-type) wafers were used as the substrates. SiO<sub>2</sub> plays a role as a gate insulator. Because the obtained solution was polar, while the SiO<sub>2</sub> surface was hydrophobic, the substrate was sonicated in a 1 M sodium hydroxide (NaOH) solution for 5 min to attach hydrophilic OH groups to its surface and thus facilitate the coating process. After treatment, the prepared precursor solution was dropped on the substrate and rotated at a speed of 3000 rpm for 30 s. The obtained samples were dried at a temperature of 100 °C for 5 min, and the coating procedure was repeated again until a desired thickness was achieved. Finally, the produced specimens were annealed for 30 min in air at various temperatures ranging from 250 °C to 800 °C for structural characterization. Thicknesses, densities, roughness values, and crystallization temperatures of the obtained thin films were determined by x-ray reflectivity (XRR) and x-ray diffraction (XRD) techniques using a Rigaku Ultima IV system with Cu K $\alpha$  ( $\lambda$  = 1.540 56 Å) radiation and cross beam optics [23–25].

To fabricate a transistor, source and drain Al electrodes with thicknesses of 200 nm were deposited on the fabricated film surface by thermal evaporation through a stencil shadow mask with various channel sizes. The channel width was set to 1000  $\mu$ m, whereas the channel length varied from 50  $\mu$ m to 350  $\mu$ m. Device characteristics of the manufactured TFTs including the output (drain current  $I_D$  versus drain-source voltage  $V_{DS}$ ) and transfer ( $I_D$  versus gate-source voltage  $V_{GS}$ ) ones were determined at room temperature and ambient pressure using a Keysight B2912A system.

All transfer characteristics were measured in the saturation regime because the produced TFTs were operated at high  $V_{DS}$  values corresponding to the saturated drain current. In this regime, the magnitude of  $I_D$  can

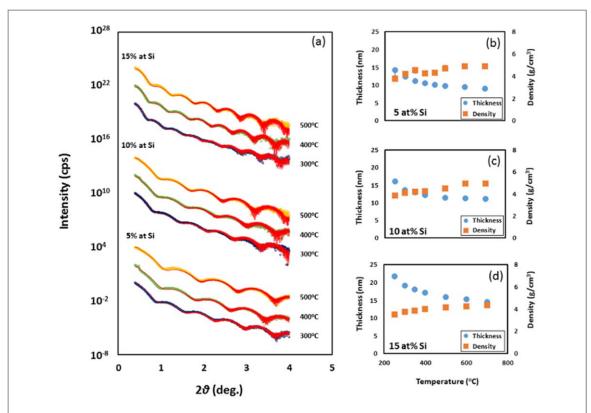

**Figure 1.** (a) XRR profiles of the ISO thin films with various concentrations of Si dopant. Their positions are aligned along the vertical direction for clarity. The experimental data points depicted by the blue, green, and orange circles were obtained for the thin films annealed at 300, 400, and 500  $^{\circ}$ C, respectively. The red curves denote the fitting data obtained with the GenX software. Using these results, film thicknesses (blue circles) and densities (orange squares) were estimated for the specimens containing (b) 5 at%, (c) 10 at%, and (d) 15 at% Si. The calculated error bars were relatively small.

be expressed as

$$I_{\rm D} = \frac{W.\mu.C_{\rm i}}{2L} (V_{\rm GS} - V_{\rm T})^2, \tag{1}$$

where  $\mu$  is the field-effect mobility,  $C_i$  is the capacitance per unit area of the gate insulator, and  $V_T$  is the threshold voltage [26]. Hence, the field-effect mobility  $\mu$  can be determined as follows:

$$\mu = \frac{2L}{W.C_{\rm i}} \left(\frac{\partial \sqrt{I_{\rm D}}}{\partial V_{\rm GS}}\right)^2. \tag{2}$$

After plotting  $\sqrt{I_D}$  versus  $V_{GS}$ , the magnitudes of  $\mu$  and  $V_T$  were estimated from the slope and intercept of the fitting line, respectively [27].

## 3. Results and discussion

#### 3.1. Effects of Si doping on the density, thickness, and crystallinity of ISO film

The XRR profiles obtained for the ISO films with Si contents of 5, 10, and 15 at% exhibit oscillations (see figure 1(a)), whose periods and amplitudes reflect their thicknesses and densities, respectively. Generally, surface roughness is related to the XRR intensity decay rate and the interface roughness is determined from the XRR oscillation decay rate at higher angles [24]. It is clear that increasing the annealing temperature increased the oscillation period.

The GenX software was used to estimate the thicknesses, densities, and roughness values of the produced films using the method described in the previous section [11, 28]. The obtained fitting data are displayed as the red curves in figure 1(a). In addition, density and thickness were plotted as functions of the annealing temperature at Si contents of 5, 10, and 15 at% in figures 1(b)–(d), respectively. As the annealing temperature increased to  $400\,^{\circ}$ C, the residues present inside the film, such as organic functional groups of the raw materials and fragments of the organic solvent, evaporated [11], reducing the film thickness and increasing the film density. After the evaporation process was complete, the film thickness and density remained unchanged regardless of the further increase in the annealing temperature. The ideal densities of the bulk ISO specimens

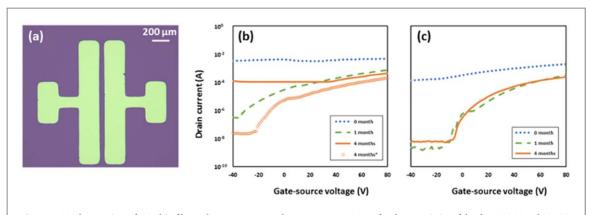

**Figure 2.** (a) The top view of ISO thin film at the  $L=50~\mu\mathrm{m}$  and  $W=1000~\mu\mathrm{m}$ . Transfer characteristics of the (b) IO TFT and (c) ISO (3 at% Si) TFT with  $L=50~\mu\mathrm{m}$  and  $W=1000~\mu\mathrm{m}$  annealed at  $500~^\circ\mathrm{C}$  in air, which were recorded at  $V_\mathrm{DS}=40~\mathrm{V}$  and various storage times, except for the orange circles in figure 2(b), which were obtained for the 4-month IO TFT at  $V_\mathrm{DS}=100~\mathrm{V}$  as a reference.

with Si contents of 5, 10, and 15 at% were 6.9, 6.7, and 6.5 g cm<sup>-3</sup>, respectively. However, as shown in the figures 1(b)–(d), the values estimated in this work were much smaller than the ideal ones. In addition, increasing the concentration of Si dopant increased the film thickness, which was consistent with the observed reduction in the film density. For instance, at an annealing temperature of 500 °C, the thicknesses of the films containing 5, 10, and 15 at% Si were around 10, 11, and 16 nm, while their densities were approximately 4.7, 4.5, and 4.1, respectively. This phenomenon can be attributed to the stabilization of the ISO amorphous structure by Si doping because stable amorphous materials typically contain networks with voids that decrease their densities [29].

The RMS roughness values of IO and ISO films estimated from XRR profiles increased with increases of Si concentration and annealing temperature, varing from 0.2 nm for as-deposited IO to 1.1 nm for ISO with 15 at% Si annealed at 1000 °C. For thin films used for TFTs annealed at 400 °C–600 °C (discussed in sections 3.2–3.5), the values are around 0.7 nm. Although they are larger than those of ISO films fabricated by DC sputtering (ca. 0.23 nm) [6], surface roughness of ISO films fabricated by spin coating in this work was much smaller than thin-film thicness ( $\geq$ 10 nm), and was small enough for aplication to the channel of TFTs.

The crystallinity of the studied ISO films was examined by performing XRD measurements. It was found that in the temperature range of up to  $800\,^{\circ}$ C, no crystalline phases were detected. In other words, the produced ISO thin films remained fully amorphous even at high annealing temperatures.

### 3.2. Effect of ageing on TFT characteristics

The top view of ISO thin film at  $L=50~\mu\mathrm{m}$  and  $W=1000~\mu\mathrm{m}$  was shown at figure 2(a), observed by an optical microscope BX53M. Figures 2 (b) and (c) illustrate the transfer characteristics of pure InO TFT (0 at% Si) and ISO TFT (3 at% Si) with the channel length  $L=50~\mu\mathrm{m}$  and channel width  $W=1000~\mu\mathrm{m}$  annealed at 500 °C in air, which were obtained at different storage times ranging from 0 month to 4 months. Although the IO TFT was conductive before storage and did not exhibit any conductance modulation by  $V_{\mathrm{GS}}$ , the latter phenomenon was observed at a  $V_T$  of about  $-34~\mathrm{V}$  after 1 month of storage. After 4 months of storage, the magnitude of  $V_T$  became very close to 0. However, after several measurements conducted under bias conditions, the TFT became conductive again, suggesting that the electronic properties of IO films were very unstable.

It is well known that in metal oxide semiconductors including  $In_2O_3$ , charge carriers are generated by the formation of oxygen vacancies [30]. Therefore, ideal  $In_2O_3$  is a good semiconductor without defects; however, it can become very conductive due to the presence of charge carriers generated by oxygen defects, which was observed in this work for the 0-month IO TFT; the formation of these defects likely occurred during the thermal evaporation stage of the electrode deposition process conducted in high vacuum. As a result, the operation of the IO TFT was observed after 1 month of storage and continued after 4 months of storage suggesting that oxygen species penetrated the thin film and gradually filled its defects. Nonetheless, after several consequent measurements, the 4-month IO TFT ceased to be a semiconductor and reversed back to the conductive mode. This behavior might result from the release of oxygen under the bias conditions due to the small dissociation energy of the In-O bond [31]; various bond dissociation energies obtained for O and several other elements including In and Si are listed in table 1.

On the other hand, although the ISO TFT also exhibited conductive behavior immediately after electrode deposition, its conductance was modulated by  $V_{\rm GS}$ . Conductance modulation became significant with an  $V_T$  of about -13 V after 1 month of storage and varied only slightly in the period between 1 month to 4 months. In both cases of IO and ISO TFTs, it can be suggested that the number of oxygen defects was reduced after storage.

Table 1. Dissociation energies of the bonds between various elements and oxygen. Adapted from Luo, CRC Handbook of Chemistry and Physics, 90th Edition [31]. Bond dissociation energy  $(kJ \text{ mol}^{-1})$ ≤250 In-O346 Ga-O374 Sn-O528 Si-O 799 C - O1076

**Table 2.** Effect of storage time on the performance of TFTs annealed at 500 °C in air.

| Sample          | Threshold voltage $V_T(V)$ | Mobility $\mu$ (cm <sup>2</sup> /Vs) | Subthreshold swing (V/dec) | On/off current ratio |

|-----------------|----------------------------|--------------------------------------|----------------------------|----------------------|

| 0-month IO TFT  | _                          | conductive                           | _                          | _                    |

| 1-month IO TFT  | -34                        | 0.80                                 | 14                         | $2 \times 10^3$      |

| 4-month IO TFT  | _                          | conductive                           | _                          | _                    |

| 0-month ISO TFT | _                          | conductive                           | _                          | _                    |

| 1-month ISO TFT | -13                        | 0.58                                 | 5                          | $2 \times 10^{5}$    |

| 4-month ISO TFT | -7                         | 0.29                                 | 4                          | $4 \times 10^4$      |

However, the ISO TFTs stored for more than one month demonstrated much better performance and were more stable than the IO TFTs, which was consistent with the results obtained for the ISO TFTs fabricated by DC sputtering due to the high dissociation energy of the Si-O bond [10], indicating that the IO TFT was less efficient in capturing oxygen during prolonged storage. The longer was the storage time, the higher was the amount of captured oxygen, and the lower was the number of oxygen vacancies, which shifted the value of  $V_T$  to a magnitude close to 0. In other words, the longer storage times contribute to the improvement of  $V_T$  and subthreshold voltage while affecting the mobility  $\mu$  and on/off current ratio. Table 2 lists the device parameters obtained for both the IO and ISO TFTs. A detailed comparison between the performances of these two devices will be conducted in the next section.

#### 3.3. Dependence of TFT characteristics on Si concentration

Figure 3 illustrates the transfer characteristics of the 1-month IO TFT (0 at% Si) and 1-month ISO TFT (3 at% Si) with the channel length  $L=50~\mu\mathrm{m}$  and channel width  $W=1000~\mu\mathrm{m}$  annealed at  $500~\mathrm{C}$  in air, which were obtained at  $V_{\mathrm{DS}}=40~\mathrm{V}$ . The ISO TFT exhibited a low off current less than  $10^{-8}$  A, which was almost equal to the limit of the utilized measurement system. On the other hand, the off current of the IO TFT was higher than that of the ISO TFT by about two orders of magnitude. In addition, the  $V_T$  of the IO TFT (about  $-34~\mathrm{V}$ ) was shifted to a magnitude close to 0 V after Si doping. These results are consistent with the phenomenon observed for DC-sputtered samples in previous studies [6–10], suggesting that the effective doping of indium oxide with Si and related reduction of the number of oxygen defects, because oxygen defects produce electron carriers, which increased the off current and absolute value of  $V_T$ .

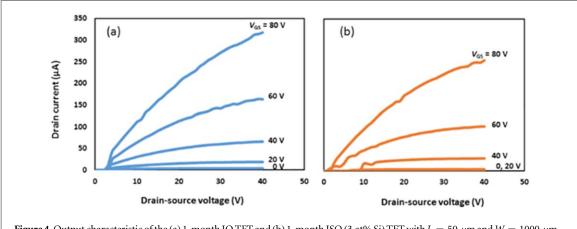

The output characteristics of the 1-month IO and 1-month ISO (3 at% Si) TFTs annealed at 500  $^{\circ}$ C in air are shown in figure 4. At low  $V_{\rm DS}$  values, the magnitude of  $I_D$  increased almost linearly with a slightly concave feature, suggesting the existence of an injection barrier between the source electrodes and the channels of the IO and ISO thin films.

The estimated values of  $\mu$ ,  $V_T$ , on/off current ratio, and subthreshold swing obtained for the IO TFT were 0.80 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, -34 V, 2 × 10<sup>3</sup>, and 14 V/dec, respectively (see table 2). For the solution-processed IO TFT fabricated by Kim *et al*,  $\mu$  was 0.04 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>,  $V_T$  was 42.6 V, the on/off current ratio was 10<sup>4</sup>, and the subthreshold swing was 23.8 V/dec [32]. In another study, a  $\mu$  of 6 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and on/off current ratio of 10<sup>3</sup> were obtained for an IO TFT fabricated by the spin coating method [33]. As of today, the best TFT performance corresponding to a  $\mu$  of to 55.26 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and on/off current ratio of 10<sup>7</sup> was reported by the Han group [22].

annealed at 500 °C in air, which were obtained at  $V_{\rm DS}=40~{\rm V}.$

Figure 4. Output characteristic of the (a) 1-month IO TFT and (b) 1-month ISO (3 at % Si) TFT with  $L=50~\mu\mathrm{m}$  and  $W=1000~\mu\mathrm{m}$ annealed at 500 °C in air.

In contrast, the solution-processed ISO TFT exhibited significantly enhanced device characteristics as compared with those of the IO TFT fabricated in this work, except for the slight decrease in  $\mu$ ; the estimated values of  $\mu$ ,  $V_T$ , on/off current ratio, and subthreshold swing were 0.58 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, -13 V, 2 × 10<sup>5</sup>, and 5 V/ dec, respectively (table 2). Since the same behavior was observed for sputtered ISO TFTs in previous works [6-10], it can be concluded that Si doping reduced the number of oxygen defects and thus improved the magnitude of  $V_T$ . However, this process might also slightly reduce the value of  $\mu$ .

### 3.4. Dependence of ISO TFT characteristics on annealing temperature

High annealing temperatures are unsuitable for solution processing since many substrates, such as glass and plastic ones, are unable to endure them. On the other hand, the results of thermal deposition spectroscopy studies [11] and dependence of the film density and thickness on the annealing temperature discussed in section 3.1 above (see figures 1(b)–(d)) suggest that organic contaminants can remain on the film surface at temperatures below 400 °C. Therefore, annealing temperatures of 400, 500, and 600 °C were selected for the TFTs fabricated in this study to remove contaminants from their surfaces as well as not too high temperatures.

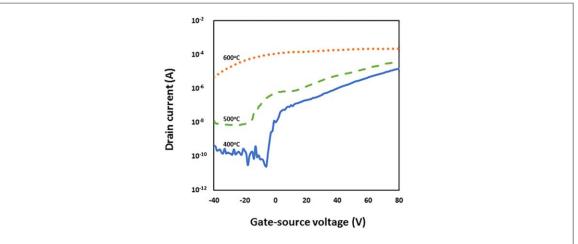

Figure 5 displays the transfer characteristic of the 4-month ISO TFTs (3 at% Si) with the channel length  $L=50~\mu{\rm m}$  and channel width  $W=1000~\mu{\rm m}$  annealed at different temperatures between 400 °C and 600 °C in air, which were obtained at  $V_{\rm DS}=40~{

m V}$ . They show that the ISO thin films exhibit higher conductivity with increasing annealing temperature, which can be attributed to the larger number of oxygen defects; this trend is similar to the effects of ageing and Si concentration discussed in sections 3.2 and 3.3 respectively. Owing to the relatively small number of oxygen defects, the TFT annealed at 400 °C demonstrated the optimal performance corresponding to a small  $V_T$  of -5 V, low off current of about  $10^{-10}$  A, small subthreshold swing of 2 V/dec, and high on/off current ratio of  $10^5$ . Only  $\mu = 0.04$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> was worse than that of the TFT annealed at 500 °C  $(0.07 \text{ cm}^2 \text{ V}^{-1} \text{s}^{-1})$ , which was likely caused by its relatively high carrier density in the on-state resulting from the presence of oxygen defects and applied  $V_{GS}$ . The device characteristics of the TFTs described in figure 5 are listed in table 3.

**Figure 5.** Transfer characteristics of the 4-month ISO (3 at% Si) TFT with  $L=50~\mu{\rm m}$  and  $W=1000~\mu{\rm m}$  annealed at various temperatures in air, which were obtained at  $V_{\rm DS}=40~{\rm V}$ .

Table 3. Dependence of the device characteristics of the 4-month ISO TFTs on the annealing temperature.

| Sample                           | Threshold voltage $V_T(V)$ | Mobility $\mu$ (cm <sup>2</sup> /Vs) | Subthreshold swing (V/dec) | On/off current ratio   |

|----------------------------------|----------------------------|--------------------------------------|----------------------------|------------------------|

| 400 °C ISO TFT<br>500 °C ISO TFT | -5<br>-15                  | 0.04<br>0.07                         | 2<br>6                     | $10^5$ $3 \times 10^3$ |

| 600 °C ISO TFT                   | _                          | conductive                           | _                          | _                      |

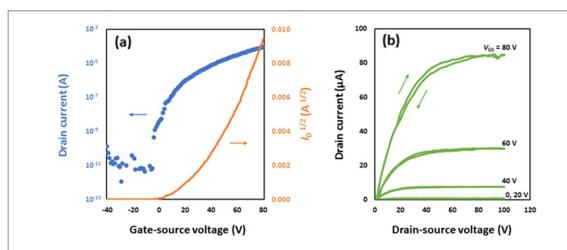

**Figure 6.** (a) Transfer characteristics at  $V_{\rm DS}=100~{\rm V}$  and (b) output characteristics obtained for the 4-month ISO (3 at% Si) TFT with  $L=50~{\rm \mu m}$  and  $W=1000~{\rm \mu m}$  annealed at 400  $^{\circ}{\rm C}$  in air.

# 3.5. Optimal performance of ISO TFTs

The results presented above revealed that the addition of a small amount of Si significantly improved the stability of the IO TFT system as well as the values of  $V_T$ , subthreshold voltage, and off current despite the slight decrease in  $\mu$ . The optimal performance of the ISO TFTs was observed at low annealing temperatures and could be characterized by two sets of parameters. To obtain low values of subthreshold swing and  $V_T$ , small numbers of oxygen defects are preferred, while their large numbers are favorable for high values of  $\mu$ . So far, to compare the parameters of the IO and ISO TFTs, their transfer characteristics were determined at  $V_{\rm DS}=40~{\rm V}$  because the IO TFT was unstable under the high bias conditions described in section 3.2. However, to estimate the operation parameters of the ISO TFTs in the saturation regime more accurately, their transfer characteristics were determined at  $V_{\rm DS}=100~{\rm V}$  to ensure that the drain current was fully saturated.

Figure 6 describes the transfer characteristics at  $V_{\rm DS}=100~{\rm V}$  and output characteristics obtained for the 4-month ISO TFTs (3 at% Si) with the channel length  $L=50~\mu{\rm m}$  and channel width  $W=1000~\mu{\rm m}$  annealed at 400 °C in air. The estimated optimal values of  $\mu$ ,  $V_T$ , on/off current ratio, and subthreshold swing were 0.21 cm² V $^{-1}$ s $^{-1}$ , -5 V,  $2\times10^7$ , and 0.5 V/dec, respectively. Among the output characteristics, the forward

and reverse drain currents were almost identical, except for the curve obtained at a  $V_{\rm GS}$  of 80 V. The hysteresis phenomenon might originate from the trap site near the interface between the channel and the gate insulator where the mobile carriers are confined at high applied  $V_{\rm GS}$ .

As indicated by the results of other works on doped IO TFTs fabricated by spin coating [34], high values of  $\mu$  are required for their satisfactory operation. Hence, further studies in this area will involve the use of different annealing environments (either containing oxygen gas or exposed to ultraviolet light in vacuum) and post-contact annealing procedures since they may enhance the performance of solution-processed metal oxide semiconductor TFTs at low temperatures [22, 35, 36]. Recent reports on detailed analysis of structure and electronic properties for other Si-doped oxides [37–39] will also help the improvement of device performance of ISO TFTs.

#### 4. Conclusions

In this work, silicon-doped indium oxide thin films were prepared by the spin coating technique. The presence of Si atoms increased the stability of the In–Si–O amorphous structure at temperatures as high as 800 °C. With increasing the Si concentration, the film thickness increased as well, while the film density decreased. Furthermore, Si doping significantly decreased the absolute value of  $V_T$  of the ISO TFT and reduced its subthreshold voltage. The 3 at% Si-doped TFT annealed at 400 °C exhibited the smallest subthreshold swing of 0.5 V/dec,  $V_T$  of -5 V,  $\mu$  of 0.21 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, and on/off current ratio of  $2 \times 10^7$ . In future, additional studies involving different annealing environments will be conducted to further improve the performance of solution-processed ISO TFTs.

# Acknowledgments

This work was partially supported by the Hyogo Overseas Research Network (HORN) Program, Hyogo Earthquake Memorial 21st Century Research Institute, and Grants-in-Aid for Scientific Research (grant No. JP15H03568). Bui Nguyen Quoc Trinh would like to acknowledge the support provided by the Vietnam National Foundation for Science and Technology Development (NAFOSTED; grant No. 103.02-2012.81).

### **ORCID** iDs

Toshihide Nabatame https://orcid.org/0000-0002-5973-0230 Akihiko Fujiwara https://orcid.org/0000-0002-1319-388X

# References

- [1] Nomura K, Ohta H, Takagi A, Kamiya T, Hirano M and Hosono H 2004 Nature 432 488–92

- [2] Kamiya T, Nomura K and Hosono H 2010 Sci. Technol. Adv. Mater. 11 044305

- [3] Kamiya T and Hosono H 2010 NPG Asia Mater. 2 15-22

- [4] Chiang H Q, McFarlane B R, Hong D, Presley R E and Wager J F 2008 J. Non-Cryst. Solids 354 2826–30

- [5] Nomura K, Kamiya T, Ikenaga E, Yanagi H, Kobayashi K and Hosono H 2013 J. Appl. Phys. 114 163713

- [6] Mitoma N, Aikawa S, Gao X, Kizu T, Shimizu M, Lin M F, Nabatame T and Tsukagoshi K 2014 Appl. Phys. Lett. 104 102103

- [7] Mitoma N, Aikawa S, Ou-Yang W, Gao X, Kizu T, Lin M F, Fujiwara A, Nabatame T and Tsukagoshi K 2015 Appl. Phys. Lett. 106 042106

- [8] Aikawa S, Nabatame T and Tsukagoshi K 2013 Appl. Phys. Lett. 103 172105

- [9] Aikawa S, Mitoma N, Kizu T, Nabatame T and Tsukagoshi K 2015 J. Appl. Phys. 106 192103

- [10] Kizu T, Aikawa S, Nabatame T, Fujiwara A, Ito K, Takahashi M and Tsukagoshi K 2016 Appl. Phys. Lett. 120 045702

- [11] Jan H E, Hoang H, Nakamura T, Koga T, Ina T, Uruga T, Kizu T, Tsukagoshi K, Nabatame T and Fujiwara A 2017 J. Electron. Mater. 46

- [12] Yu X et al 2015 Proc. Natl. Acad. Sci. USA 112 3217-22

- [13] Smith J, Zeng L, Khanal R, Stallings K, Facchetti A, Medvedeva J E, Bedzyk M J and Marks T J 2015 Adv. Electron. Mater. 1 1500146

- [14] Lee DH, Chang YJ, Herman GS and Chang CH 2007 Adv. Mater. 19 843-7

- [15] Niederberger M, Garnweitner G, Buha J, Polleux J, Ba J and Pinna N 2006 J. Sol-Gel Sci. Technol. 40 259-66

- [16] Norris B J, Anderson J, Wager J F and Keszler D A 2003 J. Phys. D: Appl. Phys. 36 L105

- $[17] \ Park \ J \ H, Yoo \ Y \ B, Lee \ K \ H, Jang \ W \ S, Oh \ J \ Y, Chae \ S \ S, Lee \ W \ H, Han \ S \ W \ and \ Baik \ H \ K \ 2013 \ ACS \ Appl. \ Mater. \ Interfaces \ 5 \ 8067-75$

- [18] Jeong S, Jeong Y and Moon J 2008 J. Phys. Chem. C 112 11082-5

- [19] Minari T, Kano M, Miyadera T, Wang S D, Aoyagi Y and Tsukagoshi K 2009 Appl. Phys. Lett. 94 093307

- $[20]\ \operatorname{Li} Y, \operatorname{Liu} C, \operatorname{Wang} Y, \operatorname{Yang} Y, \operatorname{Wang} X, \operatorname{Shi} Y \text{ and Tsukagoshi K } 2013\ AIP\ Adv.\ 3\ 052123$

- [21] Li Y, Liu C, Kumatani A, Darmawan P, Minari T and Tsukagoshi K 2011 AIP Adv. 1 022149

- [22] Han SY, Herman GS and Chang CH 2011 J. Am. Chem. Soc. 133 5166–9

- [23] Walker D E, Major M, Yazdi M B, Klyszcz A, Haeming M, Bonrad K, Melzer C, Donner W and Seggern H V 2012 ACS Appl. Mater. Interfaces 4 6835–41

- [24] Yasaka M 2010 Rigaku J 26 2

- [25] Jeong J H, Yang H W, Park J S, Jeong J K, Mo Y W, Kim H D, Song J and Hwang C S 2008 Electrochem. Solid-State Lett. 11 H157–9

- [26] Sze SM and Lee MK 2012 Semiconductor Devices: Physics and Technology 3rd edn (New York: Wiley)

- [27] Matsuoka Y, Uno K, Takahashi N, Maeda A, Inami N, Shikoh E, Yamamoto Y, Hori H and Fujiwara A 2006 Appl. Phys. Lett. 89 173510

- [28] Bjorck M and Andersson G 2007 J. Appl. Cryst. 40 1174-8

- [29] Shackelford J F and Masaryk J S 1978 J. Non-Cryst. Solids 30 127–39

- [30] Jeong S, Lee J Y, Lee S S, Choi Y and Ryu B H 2011 *J. Phys. Chem.* C 115 11773–80

- [31] Luo Y R 2009 CRC Handbook of Chemistry and Physics 90th edn, ed D R Lide (Boca Raton: CRC Press/Taylor and Francis)

- $[32] \ Kim\,H\,S, Byrne\,P\,D, Facchetti\,A\,and\,Marks\,T\,J\,2008\,\textit{J. Am. Chem. Soc.}\,\, {\color{red}130\,12580-1}$

- [33] Kim M G, Kanatzidis M G, Facchetti A and Marks T J 2011 Nature Mater. 10 382-8

- [34] Yu X, Marks T J and Facchetti A 2016 Nature Meter. 15 383–96

- [35] Cheong H, Ogura S, Ushijima H, Yoshida M, Fukuda N and Uemura S 2015 AIP Adv. 5 067127

- [36] Xu Y, Li C, Amegadze P S K, Park W T, Long D X, Minari T, Balestra F, Ghibaudo G and Noh Y Y 2014 Appl. Phys. Lett. 105 133505

- [37] Nakamura N, Kim J and Hosono H 2018 Adv. Electron. Mater. 4 1700352

- [38] Kaczmarski J, Borysiewicz MA, Piskorski K, Wzorek M, Kozubal M and Kamińska E 2018 Semicond. Sci Technol. 33 015010

- [39] Kaczmarski J, Taube A, Borysiewicz M A, Myśliwiec M, Piskorski K, Stiller K and Kamińska E 2018 *IEEE Trans. Electron Devices* 65 129–35